Future-Proof Your Designs With PCIe® Gen 6-Compliant Oscillators, Buffers and Clock Generators

Doubling in speed for each new generation, PCIe has been the interconnect standard of choice for two decades. Because our oscillators, clock generators and clock buffers exceed PCIe Gen 6 requirements and also comply with PCIe Gen 1–5, you can be confident when selecting our timing solutions for your next-generation designs.

PCIe Oscillators

Our oscillators provide a PCIe Gen 1/2/3/4/5/6-compliant clock source based on both MEMS and quartz technologies. Advantages include small package sizes and functionality across a wide range of temperatures.

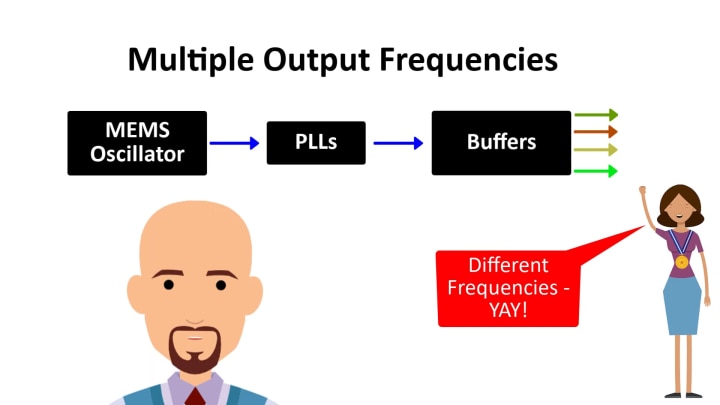

PCIe Clock Generators

Our fully integrated, single-chip solutions feature PCIe Gen 1/2/3/4/5/6 compliance, up to eight outputs, compact package sizes, wide temperature ranges and optional spread spectrum functions.

PCIe Buffers

Our PCIe Gen 1/2/3/4/5/6-compliant buffers feature ultra-low-additive, high-jitter performance for up to 12 outputs while meeting industrial temperature ranges.

PCIe Switches (Switchtec™ Technology)

Our PCIe Gen 3/4/5 reference designs for PCIe switches utilize our high-performance clocking solutions. Each design is fully tested and validated for faster time to market with reduced risk.

PCIe QuickLearn Video Series

Learn about PCIe timing by watching our six-part QuickLearn Video Series. We will cover:

- PCIe bus data transmission overview

- Widely deployed architecture

- PCIe jitter specifications ane measurement “how-to”

- Spread-spectrum clocking

- Data center and automotive applications

PCIe QuickLearn Video Series | Video #1 - PCIe Overview

PCIe® QuickLearn Video Series Video #1 - PCIe Overview: Data

This five-minute video provides the viewer with the fundamental concepts related to PCIe. It is the first video in a series that focuses primarily on the clocks and timing issues related to PCIe, and it also provides a basic understanding with which to explore further PCIe topics.

What topics are covered?

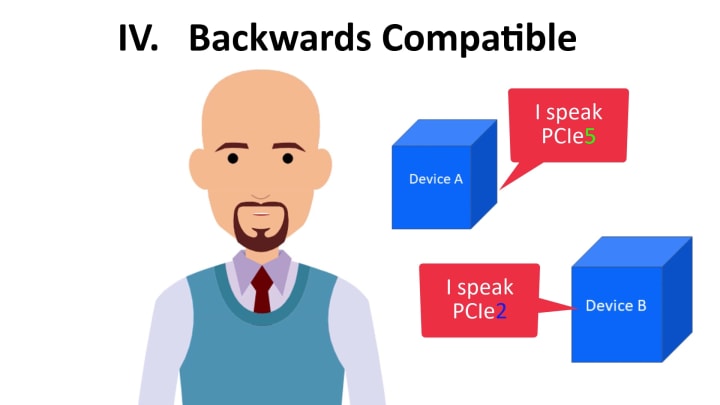

1. Point-to-point bus

2. Bi-directional bus

3. Scalability of data rates

4. Backwards compatibility

5. Wide adoption across many markets

6. Typical PCIe clock format

PCIe® QuickLearn Video Series Video #2 - PCIe Overview

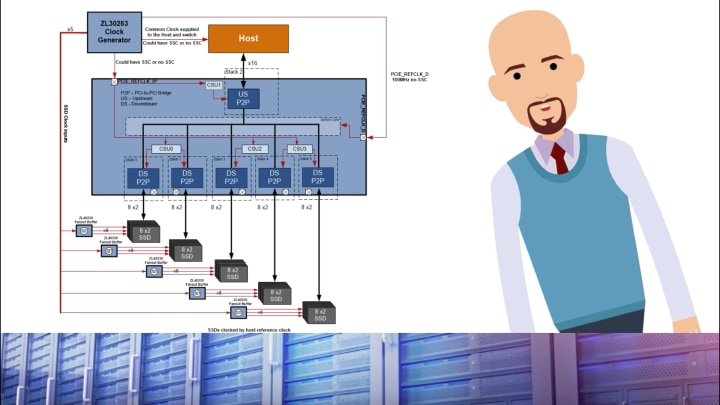

This five-minute video builds upon the previous video in this series to focus on the most widely-deployed PCIe architecture – the Common Reference Clock (or Common Clock) architecture.

What topics are covered?

1. Basic representation of the Common Clock architecture

2. Ideal Reference Clock vs. real Reference Clock

3. Modeling Transmit and Receiver filtering effects on the Reference Clock

4. Evolution of the Reference Clock jitter requirements with each new PCIe generation

PCIe® QuickLearn Video Series Video #3 - Measuring Reference Clock Jitter

This brief video explains the options for measuring real-world Reference Clock jitter to determine whether the clock meets the PCIe specifications.

What topics are covered?

1. How do I measure my Reference Clock to determine if it meets the jitter specifications?

2. Measuring with an oscilloscope

3. Measuring with a phase noise analyzer

4. Post-processing the measured data per the PCIe specification

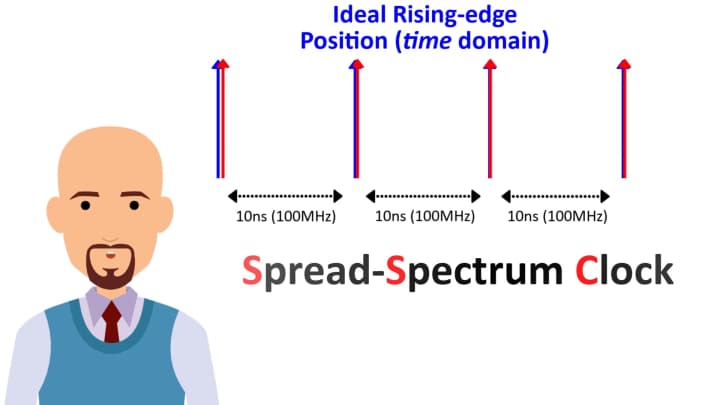

PCIe® QuickLearn Video Series Video #4 - Spread Spectrum Clocking

This five-minute video describes spread-spectrum clocking and how it applies to PCIe systems.

What topics are covered?

1. Electromagnetic Interference (EMI) explained and why it can be a problem in PCIe systems.

2. Approaches used to reduce EMI

3. Spread-spectrum clocking defined

4. Comparison of a real-world PCIe spread-spectrum clock vs. a clock without spread spectrum

PCIe® QuickLearn Video Series Video #5 - Clocks in Automobiles

This four-minute video describes the challenges of using high-speed clocks in vehicles and presents various solutions.

PCIe® QuickLearn Video Series Video #6 - Clocks in Data Centers

This five-minute video provides an overview of using the PCIe bus in data centers.

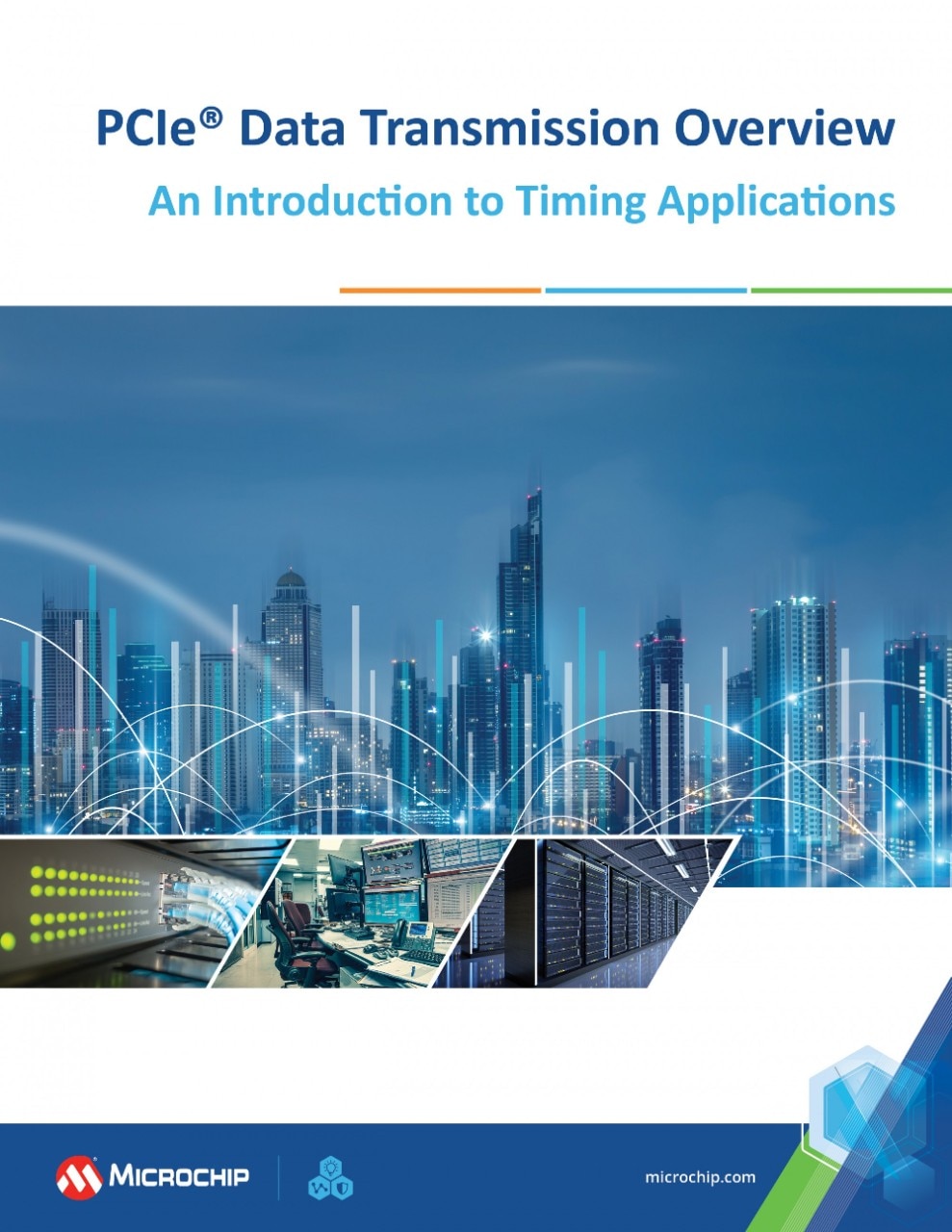

PCIe Data Transmission Overview: An Introduction to Timing Applications

Learn about the PCIe bus standard and how it is used in different applications. In this e-book, we take a look at:

- A general overview of the PCIe bus standard

- PCIe clock/data architecture and requirements

- PCIe clocks used in automobiles and data centers

Customize Your Device with ClockWorks® Configurator

With just a few clicks, you can program your devices to any combination of frequency, temperature, ppm and package size to meet your specific application’s requirements. You can also use this tool to download customized data sheets and order custom samples with a 48-hour turnaround.

- Application Notes

- Brochures

|

Title

|

|

|---|---|

| ANTC203 - ANTC203 - PCI Express ? Signal Integrity and EMI | Download |

| Interfacing Timing Devices to Switchtec Devices | Download |

| ZLAN-711 ZL3026x Family PCIe4 Compliance Testing Results | Download |

| ZLAN-806 PCIe Reference Clock Crossing Point Optimization | Download |

| ZLAN-809 Preconfigured ZL30265s for Switchtec Applications | Download |

|

Title

|

|

|---|---|

| PCIe Clock & Timing Sell Sheet | Download |

Need Some Help?

We are here to support you. Contact our Client Success Team to get assistance with your design.